# Growth and electrical characterization of thin film silicon on MG-Si for solar cell applications

D. M. Danielsson RH-09-2009

Jón Tómas Guðmundsson tumi@raunvis.hi.is Science Institute, University of Iceland Dunhagi 3, IS-107 Reykjavik

# Growth and electrical characterization of thin film silicon on MG-Si for solar cell applications

by

# Davíð Már Daníelsson

A thesis submitted in partial satisfaction of the requirements for the degree of Master of Science in Electrical Engineering at the University of Iceland

Committee in charge:

Prof. Jón Tómas Guðmundsson, Chair

Dr. Halldór Guðfinnur Svavarsson Prof. Einar Örn Sveinbjörnsson Reykjavík June, 2009 Growth and electrical characterization of thin film silicon on MG-Si for solar cell applications

M.S. Thesis 60 ECTS

© Davíð Már Daníelsson, 2009

Faculty of Electrical and Computer Engineering School of Engineering and Natural Sciences University of Iceland Hjardarhaga 2-6 107 Reykjavik, Iceland Telephone + 354 525 4000

Printed by Leturprent Reykjavik, Iceland 2009

#### Abstract

Thin films of silicon for solar cell applications were grown by liquid phase epitaxy (LPE). The films were grown on semi-insulating single-crystalline silicon, p-type single-crystalline silicon and metallurgical grade silicon (MG-Si). MG-Si substrates have higher impurity concentrations than traditional electronic grade silicon and are used as low-cost alternatives to single crystalline substrates. p-n junctions were prepared by growing n-type silicon on p-type MG-Si substrates. The as-grown samples were hydrogenated to improve their electrical quality. Electrical characterization along with a morphology study was made on the grown samples. It was demonstrated that it is possible to produce a low-cost solar cell using metallurgical grade silicon substrates. However, hydrogenation is essential to achieve the desired electrical properties.

#### Úrdráttur

Punnar kísilhúðir fyrir notkun í sólarhlöð voru ræktaðar úr vökvafasa með LPE tækni. Húðir voru ræktaðar á hálfeingangrandi einrkristallaðan kísil, p-leiðandi einkristallaðan kísil og MG-kísil. MG-kísil undirlög innihalda hærri styrkleika af óhreinindum en kísill sem notaður er í hálfleiðaraiðnaði. Þau eru því ódýr valkostur við einkristölluð undirlög. p-n samskeyti voru útbúin með ræktun n-leiðandi kísils á p-leiðandi MG-kísil undirlög. Ræktuðu sýnin voru vetnisíbætt til að bæta rafeiginleika þeirra. Rafeiginleikar og yfirborðshrjúfleiki voru mældir fyrir ræktuðu sýnin. Sýnt var fram á að MG-kísil undirlög eru mögulegur kostur í framleiðslu á ódýrum sólarhlöðum. Hinsvegar er vetnisíbæting nauðsynlegt skref til að fá fram æskilega rafeiginleika.

# Contents

| 1 | Intr  | oduction                                             | 1  |

|---|-------|------------------------------------------------------|----|

| 2 | Silie | con solar cells                                      | 5  |

|   | 2.1   | Solar energy                                         | 7  |

|   | 2.2   | Historical overview and development                  | 9  |

|   | 2.3   | Alternative materials and methods                    | 1  |

|   | 2.4   | Silicon                                              | 4  |

|   |       | 2.4.1 Crystallinity and defects                      | 4  |

|   |       | 2.4.2 Manufacturing methods                          | 5  |

|   | 2.5   | Electrical characteristics                           | 8  |

|   |       | 2.5.1 Semiconductors and p-n junctions               | 8  |

|   | 2.6   | Creation of an active layer                          | 29 |

| 3 | Exp   | erimental methods and apparatus 3                    | 1  |

|   | 3.1   | Liquid phase epitaxy                                 | 32 |

|   |       | 3.1.1 Alternatives to LPE                            | 35 |

|   |       | 3.1.2 Doping and precipitation from the liquid phase | 37 |

|   |       | 3.1.3 Silicon LPE                                    | 11 |

|   |       | 3.1.4 LPE apparatus                                  | 15 |

|   | 3.2   | Hydrogenation of the as-grown silicon                | 17 |

|   | 3.3   | Metal contacts on semiconductors                     | 18 |

|   | 3.4   | Measurements of minority carrier lifetime            | 60 |

|   | 3.5   | Current-voltage measurements                         | 52 |

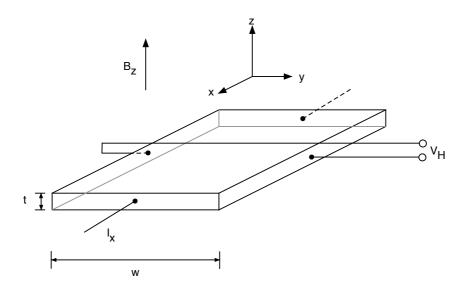

|   | 3.6   | Hall effect                                          | 53 |

|   | 3.7   | SEM & AFM                                            |    |

iv CONTENTS

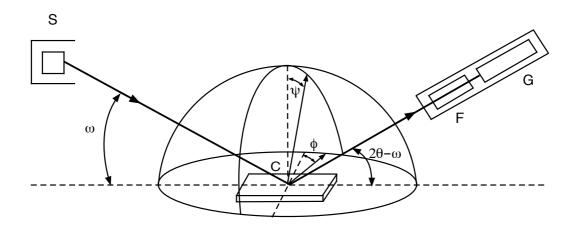

|   | 3.8 | XRD                         | 57 |

|---|-----|-----------------------------|----|

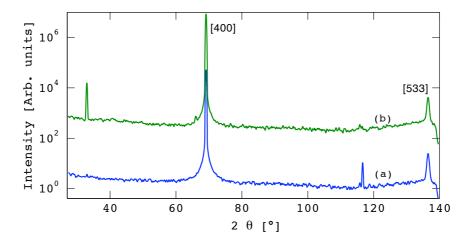

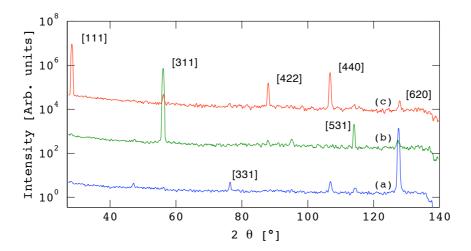

| 4 | Res | ults and discussion         | 61 |

|   | 4.1 | Substrate preparation       | 61 |

|   | 4.2 | LPE growth parameters       | 62 |

|   | 4.3 | Growth characterization     | 63 |

|   | 4.4 | Electrical characterization | 71 |

| 5 | Cor | nclusion                    | 79 |

# Chapter 1

# Introduction

In the year 2006,  $1.8 \times 10^{13}$  kWh of electrical energy were consumed in the world (E.I.A, 2009). The consumption had increased on the average 3.14% per year over the past two decades. A vast majority of the energy or about two thirds was produced by burning fossil fuels. The interest in renewable energy sources, one of which is solar energy, is continuously growing. Solar energy is one of the most abundant natural sources of energy available to mankind. It can be utilized with photovoltaic devices which can be fabricated from various materials and with various methods. Photovoltaic devices, often referred to as solar cells, convert solar energy directly into electricity. A semiconductor with an appropriate bandgap is used to absorb the photons from the sunlight and generate free charge carriers, electrons and holes. Additionally a mechanism, such as a p-n junction is needed to separate the charge carriers which allows an electric current to flow and be utilized. Solar cells are connected together to form modules to increase the output voltage and current and thus the available power.

The use of solar cells as an energy source/supply is relatively low at this time

2 Introduction

or around 0.03% of the global energy production in the year 2006 (E.I.A, 2009). It is expected that this number will rise rapidly in the coming years. The development of solar cells is rapid with continually increasing performance and reduced cost (Swanson, 2007). Currently, photovoltaics is one of the fastest growing energy sectors with 40-50% annual growth during the past five years (Green, 2007; Butler, 2008; Service, 2008). The growth of the photovoltaics industry is mainly driven by silicon based solar cells, in particular poly-crystalline silicon (Braga et al., 2008). Electricity produced from solar cells still costs about five times more than electricity produced with coal, but economics of scale are expected to close the gap by mid next decade (Shaheen et al., 2005; Swanson, 2007; Service, 2008). For photovoltaic technology to compete economically with conventional means of producing electricity the cost of module production has to be reduced to USD 0.33/Watt with module efficiency of roughly 15% (Catchpole et al., 2001). For comparison, the production cost of a module in the year 2007 was USD 3-4/Watt (Slaoui and Collins, 2007).

Solar cells can be made from various types of semiconducting materials, which can be amorphous, polycrystalline or single-crystalline. The semiconductors include silicon, III–V semiconductors such as GaAs and InP and the chalcopyrite compound copper indium gallium diselenide (CIGS) and CdTe. In addition, organic materials, including polymers, have gained attention lately. An in-depth discussion about solar cell materials is given in chapter 2.3. Silicon solar cells remain the dominant technology in the market due to the natural abundance of silicon, its high reliability, ease of processing and high efficiency. Currently 94% of all produced solar cells are made of silicon, whereof 38% is single-crystalline, 49% is poly-crystalline, 4% is amorphous and 3% is silicon ribbons (Miles et al., 2007).

Solar grade silicon wafers are produced by costly silicon purification ingot

growth and dicing process. Roughly half of the cost of a crystalline silicon solar module lies in the cost of the silicon itself (McCann et al., 2001). This has led to extensive research on thin film silicon solar cells. In particular, thin film silicon solar cells fabricated on low cost substrates are an attractive option for the market. At present silicon thin film modules are mainly based on amorphous silicon, either in a multijunction or multiple junction configuration (Green, 2007). However, there is currently active research on the growth of crystalline silicon thin films for solar cell applications (Bergmann, 1999).

Epitaxial layers of silicon have been grown on a single-crystalline Si substrate (Majumdar et al., 2003; Blakers et al., 1992; Zheng et al., 1996). In order to reduce the amount of silicon used, and thus the cost, thin films have been grown on cast metallurgical-grade (MG) poly-crystalline silicon substrate by liquid phase epitaxy (LPE) (Ciszek et al., 1993). Yamamoto et al. (1999) and Catchpole et al. (2001) discussed growth of thin film poly-Si films on glass substrates at low temperatures. Other developments of new silicon based structures for solar cell applications include low cost mechanically flexible solar cells made from ultra thin single-crystalline silicon (Yoon et al., 2008; Fan and Javey, 2008) and growth of silicon nanowire arrays (Peng et al., 2005; Garnett and Yang, 2008). Recently the application of nanodefect engineering to reduce the electrical activity of metallic impurities of a dirty silicon has been demonstrated (Buonassisi et al., 2005) which is one further attempt to eliminate the dependence on high-quality silicon feedstock. The motivation for this current work is mainly the need for inexpensive raw materials for solar cell production. By using metallurgical grade silicon as a substrate for p-n junction solar cells, the total production cost can be reduced and thereby lowering the cost per module unit area. However, it is clear that the efficiency of solar cells is being traded for cost.

4 Introduction

Here we grow silicon thin films on crystalline silicon and metallurgical grade silicon by LPE. Subsequently the as grown samples are exposed to hydrogen plasma in order to passivate defects. The quality of the grown films is assessed by electrical characterization along with a morphology study. The historical developments of silicon solar cells and the production methods applied to manufacture silicon solar cells are reviewed in chapter 2. Chapter 2 also discusses the characteristic parameters used to describe solar cells. Chapter 3 discusses the technology behind LPE growth as well as the methods used to characterize the grown films. The growth of thin film silicon, and their electrical, structural and morphological properties are discussed in chapter 4.

# Chapter 2

# Silicon solar cells

Solar cells are mainly made of semiconductors. Silicon is the most commonly used material because it exists in large quantities as silicon dioxide (sand, quartz, silica), it is inexpensive compared to other semiconducting materials and is non-toxic. However, a large disadvantage is that silicon has an indirect bandgap which results in a lower photon absorption when compared with direct bandgap materials. A discussion of other materials used for solar cells is in given in chapter 2.3.

A conventional solar cell is fabricated from inorganic semiconducting materials such as crystalline silicon (c-Si). Traditionally, the silicon is purified to a high level, grown into a single crystal ingot, sliced into wafers and then doped to form a p-n junction. Solar cells can be considered a modular power source. A typical cell with a surface area of 1 cm<sup>2</sup> produces less than half a watt of power at its peak maximum. Several of these cells are connected in serial or parallel and encapsulated to form a module. Additional devices are used for voltage inversion and regulation. Figure 2.1 shows a poly-crystalline silicon substrate along with a solar module with antireflection coatings and electrical connections. Currently the production of solar

**Figure 2.1:** On the left is a poly crystalline silicon substrate and on the right is a poly-crystalline silicon solar cell with antireflection coatings and a bus bar.

cells is dominated by the use of single-crystalline and poly-crystalline silicon modules which account for 94% of the market (Miles et al., 2007). These devices are based on silicon wafers and are commonly being referred to as the first generation (I) of photovoltaics technology (Green, 2002, 2003). The first generation cells are single junction cells that have a maximum theoretical power conversion efficiency limit of 29% which occurs at a bandgap of 1.5 eV (Stone, 1993).

The second generation (II) technologies are based on thin films that do not require the use of silicon wafers as a substrate, and thus require much less silicon as compared to the first generation cells, which leads to a significant cost reduction. The aim of the II generation cells is thus to lower the production costs of current cells often by introducing new materials and substrates (Green, 2003). The objective by the third generation (III) solar cells is to improve the electrical efficiency of the second generation cells and to lower the production costs. The third generation technologies are often separated into two categories. The first, IIIa, are novel techniques that are developed to achieve very high efficiencies. The energy conversion

2.1 Solar energy 7

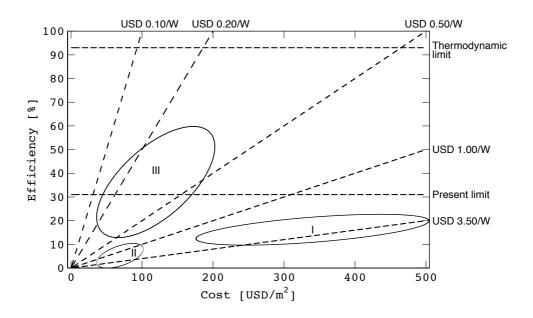

**Figure 2.2:** Cost - efficiency analysis for the three generation of solar cells. The cost is in year 2003 US dollars. Redrawn from Green (2003).

can at least double and approach the thermodynamic limit of 93% (Green, 2003). The goal of the second category of third generation devices, IIIb, is to reach moderate efficiencies at reasonable cost. Figure 2.2 shows an cost-efficiency analysis for the three generations of photovoltaics technology. Shown in the graph are possible production costs per unit cell area for each solar cell generation and the respective efficiency range (Green, 2003). The work discussed here falls under second generation technology.

# 2.1 Solar energy

For an accurate comparison of the efficiency of solar cells at different locations, a standard reference spectrum is used for radiation outside the earth's atmosphere and at the earth's surface. For photons to reach the surface of the earth, they must pass through the earth's atmosphere. The length of the path depends on the relative

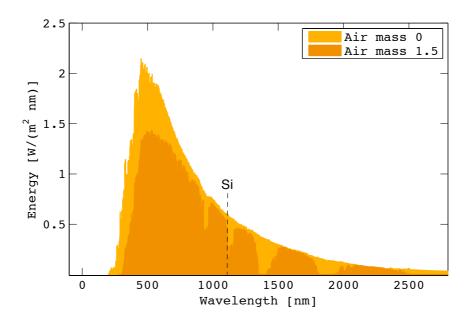

**Figure 2.3:** The AM0 and AM1.5 solar spectrum (NREL, 2008). The bandgap energy of silicon is marked in as a reference.

position of the sun and the observer. The air mass value is a measure of the air mass that the solar radiation has to travel through. Air mass zero (AM0) represents radiation outside of the earth's atmosphere and is defined to be equal to the solar constant, which is referred to as the total incoming solar electromagnetic radiation per unit area. The solar constant is equal to  $1366.1 \text{ W/m}^2$  (it fluctuates with the distance between the earth and sun). The standard conditions for comparing solar cells is the AM1.5 spectrum and refers to when the sun is at  $48.19^{\circ}$  above horizon giving a power density of  $1000 \text{ W/m}^2$ . The AM0 and AM1.5 spectrums can be seen in figure 2.3. The standard reference temperature used when measuring the efficiency of solar cells and other relevant parameters is  $25^{\circ}$  C (Green et al., 2009). A significant part of the incoming radiation is reflected off the surface of the solar cell. For silicon solar cells, this is approximately 30% of the incident light in the spectral range where silicon is photosensitive (Aroutiounian et al., 2004). Antireflection

coatings are added to the surface to minimize the amount of photons that are reflected off the surface. McCann et al. (2001) discusses surface texturization in order to increase the optical confinement. This is often done chemically by wet etching. If care is taken to maximize the optical confinement, conversion efficiency up to 17% can be achieved with active layer thicknesses as low as  $1\mu$ m (Brendel and Scholten, 1999).

# 2.2 Historical overview and development

The first practical solar cell was developed at Bell laboratories in 1954 (Chapin et al., 1954). This first solar cell was a p-n junction solar cell in which a thin layer of p-type silicon was grown on an n-type silicon substrate. It had an efficiency of 6%. Since then, the production cost of solar cells has decreased continuously and the performance increased. In 1979 the module cost was USD 32/Watt and by 2002

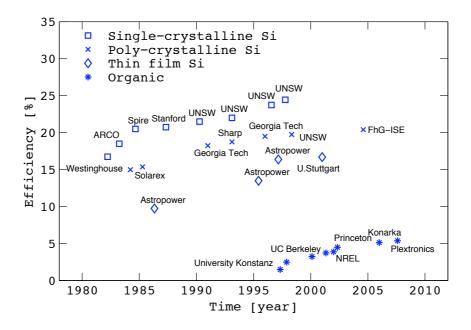

Figure 2.4: Record efficiencies of various types of solar cells (Green et al., 2009).

the module cost had decreased dramatically to USD 3.10/Watt (Swanson, 2007). As of 2007, the best single-crystalline silicon solar cells have reached an efficiency of 25.0% (Green et al., 2009) which is not far from the theoretical maximum value of 29%. An overview of the progress in efficiencies of those types of solar cells over the past several decades can be seen graphically in figure 2.4. Pictured there are the highest efficiency values measured for laboratory solar cells for various types of silicon solar cells as well as organic polymer solar cells. For comparison, the efficiency of commercially available solar cells is in the range of 10–15%. It can be seen that the efficiency is highest for single-crystalline Si solar cells, but lower for poly-crystalline silicon due to effects of grain boundaries on current transport. It is also shown that the efficiency of thin film Si is lower than for single-crystalline Si. However, the efficiency of thin films is higher with respect to the amount of silicon used. Table 2.1 gives an overview of the highest efficiencies achieved, open-circuit voltage and current density for various types of solar cells. A further discussion about efficiency and how it is defined is given in chapter 2.5.1.

**Table 2.1:** Highest confirmed data measured under AM1.5 spectrum conditions at 25°C (Green et al., 2009).

| Туре                   | Efficiency [%] | Area <sup>a</sup> [cm <sup>2</sup> ] | $V_{\rm oc} [V]$ | $J_{\rm sc} \ [{\rm mA/cm^2}]$ |

|------------------------|----------------|--------------------------------------|------------------|--------------------------------|

| Silicon                |                |                                      |                  |                                |

| Si (crystalline)       | $25.0 \pm 0.5$ | $4.00 \; (da)$                       | 0.705            | 42.7                           |

| Si (multi-crystalline) | $20.4 \pm 0.5$ | 1.002 (ap)                           | 0.664            | 38.0                           |

| Si (thin film)         | $16.7 \pm 0.4$ | 4.017 (ap)                           | 0.645            | 33.0                           |

| Si (amorphous)         | $9.5 \pm 0.3$  | $1.070 \; (ap)$                      | 0.859            | 17.5                           |

| III-V                  |                |                                      |                  |                                |

| GaAs (crystalline)     | $26.1 \pm 0.8$ | 0.998 (ap)                           | 1.038            | 29.7                           |

| GaAs (thin film)       | $26.1 \pm 0.8$ | 1.001 (ap)                           | 1.045            | 84.6                           |

| InP (crystalline)      | $22.1 \pm 0.7$ | 4.02  (at)                           | 0.878            | 29.5                           |

| Thin film chalcogenide |                |                                      |                  |                                |

| CIGS (cell)            | $19.4 \pm 0.6$ | 0.994 (ap)                           | 0.716            | 33.7                           |

| Organic                |                |                                      |                  |                                |

| Organic polymer        | $5.15 \pm 0.3$ | 1.021 (ap)                           | 0.876            | 9.4                            |

$<sup>\</sup>overline{a}$ : (ap) = aperture area, (t) = total area, (da) = designated illumination area.

The most important factors in the development of solar cells are their efficiency and their production cost. A critical factor affecting the efficiency is the minority carrier lifetime. The minority carrier lifetime is a measure of how much of the injected carriers can contribute to the electric current and it will be defined further in section 2.5. For highly efficient solar cells, the largest cost lies in the refinement of the silicon used in the production. In the refinement process, the silicon has to be melted and re-crystallised for the silicon to become single-crystalline. This processing step requires significant amount of energy.

## 2.3 Alternative materials and methods

There are various other materials and methods that have been used for research and development of solar cells. These materials can roughly be divided into organic and inorganic materials. The organic materials include polymers which have the potential of being produced inexpensively (Shaheen et al., 2005). The inorganic materials include silicon (single-crystalline, multi-crystalline, amorphous, micro-crystalline, ribbon), the chalcopyrite compound copper indium gallium diselenide (CIGS), the III–V compound semiconductors and lastly CdTe. In general, the organic materials are less expensive and easier to manufacture than the inorganic materials (Shaheen et al., 2005). However they suffer from lower efficiency and shorter minority carrier lifetimes.

The III–V materials, such as GaAs, InP and GaSb, have the advantage over silicon that they have a direct energy bandgap, high optical absorption coefficients, good minority carrier lifetimes, high mobilities (for crystalline materials) and thus the potential to be made into highly efficient solar cells. The disadvantage of the III–V compounds is that the cost of producing high quality substrates and epitaxial layers is high, which gives silicon a head start. Table 2.2 gives an overview of the

**Table 2.2:** An overview of the advantages and disadvantages of using silicon for solar cells instead of other materials.

| Advantages                                                                                                                                                                            | Disadvantages                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inexpensive and abundant Possible to use inexpensive MG-Si substrates Very well established and high reliability Ease of processing Non-toxic High quality oxide for isolation layers | Narrower bandgaps than for example GaAs and CdTe  Lower efficiency due to indirect bandgap  Relatively low electron mobility compared with semiconductors such as Ge, GaAs, GaSb, InP and InAs |

advantages and disadvantages of using silicon over other semiconductors in solar cell applications. Amorphous silicon (a-Si), CdTe and CIGS have bandgaps in the range 1.1 - 1.7 eV, so they are near the optimum bandgap energy for photovoltaic solar energy conversion (1.5 eV) by a single junction cell (Miles et al., 2007).

Multi-crystalline silicon is made by melting silicon and then allowing it to cool down in a rectangular container. An advantage of this method over the standard Czochralski method, commonly used to growth single crystalline silicon ingots, is the higher packing density per wafer area and much lower costs when compared with the traditional circular wafers. Multi-crystalline sheets and ribbons can also be fabricated by pulling the sheets from a silicon melt. An obvious advantage of this method is that the sawing can be avoided altogether. Bell and Kalejs (1998) discuss several techniques for growing silicon sheets as substrates for solar cells. This method provides an efficient use of silicon. An example of new silicon based structures for solar cell applications are low cost mechanically flexible solar cells made from ultra thin single-crystalline silicon (Yoon et al., 2008; Fan and Javey, 2008).

Solar cells made of thin film a-Si are produced with plasma enhanced chemical vapor deposition (PECVD) with silane as the source for silicon. The silicon layers can be deposited onto both glass and flexible substrates as the processing temperature can be relatively low. The amorphous silicon is hydrogenated where the hydrogen passivates the dangling bonds that result from the random arrangement of the silicon atoms (referred to as a-Si:H) in contrast to crystalline silicon (c-Si). Hydrogenated amorphous silicon has a direct optical band-gap of 1.7 eV and an optical absorption coefficient greater than  $10^5 \, \mathrm{cm}^{-1}$  for photons with energy greater than the bandgap. Therefore the thickness of the film needs only to be a few nanometers in order to absorb most of the incident light. With this method, material usage can be reduced and therefore the cost. However, the efficiency is relatively low, the highest reported only 9.5%.

Single junction Si solar cells can lose up to 56% of the available energy due to the fact that photons with energy less than the bandgap are not absorbed and photons with energy higher than the bandgap contribute to heating of the cell. Multijunction solar cells were created to minimize these effects and increase the efficiency. In 1990 a GaAs/GaSb multijunction cell was created that had an efficiency greater than 30% (Miles et al., 2007). Since then multijunction cells using for example GaInP, GaInAs on a variety of substrates have been shown to have efficiency greater than 39% (Miles et al., 2007). However, these are very expensive to manufacture. Solar cells based on CdTe and CdS have been shown to have efficiencies up to 16.5%. The CdTe layers need only to be a few microns thick, which lowers the material costs. CIGS solar cells have a direct bandgap and a high optical absorption coefficient (Mickelsen et al., 1984) and therefore the layers can be thin in order to absorb the incident light. CIGS solar cells have been fabricated with efficiencies up to 19.5% and module efficiencies up to 13.4%.

## 2.4 Silicon

Silicon exists in various forms that include single crystalline, poly-crystalline or amorphous. In this work, we use metallurgical-grade silicon (MG-Si) which is relatively impure poly-crystalline silicon which is described further in section 4.1.

## 2.4.1 Crystallinity and defects

An ideal single crystal has a lattice structure that is continuous and unbroken and a replica of the fundamental lattice structure that represents the particular crystal structure. All unit cells in the crystal structure have the same orientation. Polycrystalline or multi-crystalline materials are composed of many small crystals called grains. Multi-crystalline silicon is processed silicon where the material consists of crystal grains that are typically several millimeters in size. Metallurgical grade silicon (MG-Si) is multi-crystalline silicon that has not been purified and thus it contains a higher concentration of impurities than all the other types. The grains can be oriented randomly or they can have a preferential direction and the material is said to have a texture. Grain boundaries are the regions between the grains. The boundaries are considered to be interfacial defects as they tend to decrease the electrical and thermal conductivity.

All silicon is impure to a certain degree and contains a relatively large amount of defects. A defect can be either an imperfection in the crystal lattice or an impurity that is either added intentionally or was previously in the crystal. Defects can act as recombination centers and trap charge carriers. Point defects can be vacancies or interstitials. An impurity point defect can be substitutional or interstitial. Often defects are created during growth, which depends on the growth conditions and the nucleation site used.

There are three main grades of purity for silicon. The purest is electronic grade

2.4 Silicon

silicon (EGS) which is 9-11N. Then it is solar grade silicon which is 5-7N and finally MG-Si which is around 2N. Along a grain boundary, the atoms are bonded less regularly than within the grains and therefore carriers can get trapped there. Grain boundary atoms also tend to be more chemically active than those within the grains and thus can act as nucleation sites during growth.

## 2.4.2 Manufacturing methods

The production cost of a solar cell is composed of the manufacturing cost, cost of materials and the type of system. Two important factors regarding solar cells today are cost and efficiency, but ultimately the important parameter is the cost per watt of electrical energy produced. Silicon is widely available in nature which makes the fabrication of raw silicon relatively inexpensive. The purification of the silicon for use in solar cells, is however the most expensive part of the process.

The production process of silicon starts with a reaction of high-purity quartz with wood charcoal or coal, in an electric arc furnace. In this carbothermic process, the temperatures exceed 1900°C and the carbon reduces the silica to silicon according to

$$SiO_2 + C \rightarrow Si + CO_2$$

or

$$SiO_2 + 2C \rightarrow Si + 2CO$$

At the bottom of the furnace, the liquid silicon is cooled down, and the product is multi-crystalline metallurgical-grade silicon referred to as MG-Si. Typical MG-Si chunks are shown in figure 2.5. It contains a relatively large amount of impurities (1–2 %wt) which would normally affect the electrical performance of devices. The main impurities in MG-Si are aluminum (500 ppm), boron (30 ppm), phosphorous

(39 ppm), calcium (92 ppm), iron (230 ppm) and oxygen (4000 ppm) (Wan et al., 2006; Morvan and Amouroux, 1981). The next step in the process of purifying the silicon is mixing HCl with pulverized MG-Si to form trichlorosilane (SiHCl<sub>3</sub>). Most of the impurities are removed by distillation of the trichlorosilane liquid. A hydrogen reduction reaction is then applied to obtain solid silicon. The resulting material is 99.999% (5N) pure polycrystalline silicon and has impurity concentrations of the order of few parts per billion. To obtain single crystal silicon of still higher purity, the Czochralski technique is generally used (Pearce, 1988). It is based on melting the electronic grade silicon and re-crystallizing it by pulling a seed crystal from the melt. Often an external magnetic field is used to control the amount of unwanted impurities (Sze, 2002). The float-zone process can be used instead of the Czochralski technique to grow single crystal ingots and the resulting ingots have lower impurity concentration than those grown with the Czochralski technique and longer carrier lifetimes, if multiple passes are performed along the rod (Sze, 2002). In that case a high purity poly-crystalline silicon rod is rotated in a chamber in an argon atmosphere. A seed crystal placed at the bottom of the rod determines the crystal orientation. A radio-frequency induction heater is used to melt a portion (zone) of the rod, and moves upwards. A single crystal grows as the melt solidifies below. This method allows for more purification than the Czochralski process by doing multiple passes of the heater along the ingot. The latter method is referred to as zone-refining. Braga et al. (2008) gives an overview of the current status of production of solar-grade poly-crystalline silicon. By using wafers made from MG-Si instead of wafers made from solar grade silicon as a substrate for a solar cell, the cost can be reduced dramatically. Upgraded metallurgical grade silicon (UMG-Si) is produced by leaching and purifying MG-Si followed by a casting process. The result is a multi-crystalline silicon, about three orders of mag2.4 Silicon

nitude less pure than SGS, or 2-4N (Einhaus et al., 2000). The leaching process is based on detecting impurities such as Fe, Al, Ti and O and vary their proportions (Hötzel et al., 2000). The presence of transition metals in silicon is known to decrease the minority carrier diffusion length (Davis et al., 1980). Buonassisi et al. (2005) show that the predominant metal nano defect in multi-crystalline silicon is  $FeSi_2$  ( $\sim 20-30$  nm in diameter) and they are found in both grain boundaries as well as structural defects in grains. Also  $Fe_2O_3$  clusters, several micrometers in size are observed. They suggest that if the majority of the transition metals can be contained in micrometer-sized inclusions, and the average distance between the inclusions is kept large enough they cannot interact and therefore they do not have direct impact on the minority carrier diffusion length.

Prior to 2002 the wafer thickness for solar cell production had decreased from

**Figure 2.5:** The MG-Si rocks that were used as the starting materials for the substrates. In a traditional process, they are melted and re-crystallized to produce solar-grade silicon.

$500 \,\mu\mathrm{m}$  to  $300 \,\mu\mathrm{m}$ , which is still considered relatively thick. Shortages of silicon affecting the industry in 2004 pushed wafer thicknesses further down and as of 2007 the wafer thickness for some manufacturers was  $200 \,\mu\mathrm{m}$  or thinner (Swanson, 2007). Existing photovoltaic technologies use relatively thick silicon wafers of high purity single-crystalline silicon. The use of poly-crystalline silicon is increasing and it is currently the dominating material for solar cells (Braga et al., 2008; Miles et al., 2007). For that reason it is being investigated how it is possible to decrease the amount of silicon used instead of focusing on improving the performance. By using thinner wafers, materials costs can be reduced because most of the optical absorption takes place in the upper  $30 \,\mu\mathrm{m}$  of the grown film (Poortmans and Arkhipov, 2007).

## 2.5 Electrical characteristics

Here, we describe the main principles behind the operation of the solar cell and p-n junctions in semiconductors. First we discuss charge carriers in semiconductors, then charge transport in semiconductors, and finally p-n junctions and solar cells.

## 2.5.1 Semiconductors and p-n junctions

There are two types of charge carriers in semiconductors: electrons and holes. The electron carries a negative charge and the hole (which is always located at the site of a missing electron), behaves as if it is carrying a positive charge. Electrons move in opposite directions of holes in the presence of an electric field. A pure semiconductor crystal, such as silicon does not have available free electrons for current conduction at zero temperature, that is, the conduction band is empty and the valence band is full. At higher temperatures the thermal energy of the crystal

is sufficient to break electron bonds for some conduction to take place. Silicon is of valence 4 and if atoms of valence 5 are added to the silicon crystal, it is easy to ionize and it creates free electrons. Such atoms are referred to as donors. Similarly, adding atoms of valence 3 to silicon crystals leads to holes in the valence band. Such atoms are referred to as acceptors. These extra electrons are added to the conduction band and are available for electron conduction. As said before, a hole is a vacant site of an electron in the valence band and when electrons and holes have a close encounter they recombine. An electron-hole pair can be created by removing a bound electron from a neutral atom. In a pure semiconductor, the minimum energy required to create an electron-hole pair is equal to the bandgap energy of the semiconductor. Electron-hole pairs are created by thermal vibrations of the crystal at any non-zero temperature and also by absorption of photons that have energy above the bandgap energy. The latter is the process that is behind the operation of the solar cell. The production rate of electron-hole pairs is proportional to the intensity of the incident light.

Charge carriers can move under two influences: carrier drift and carrier diffusion. A potential difference between two points in a semiconductor creates an electric field between the two points. The charged carriers, either the electrons or the holes, will be accelerated due to the field until they hit a scattering center. The carriers will have average drift velocity along the lines of the electric field. How easily the charges can move through the crystal structure in the presence of an electric field is described by a parameter referred to as mobility. Scattering of electrons can affect the transport of charge carriers and therefore the mobility. Scattering lowers the energy and momentum of the carriers. Two scattering mechanisms worth mentioning are impurity scattering and lattice scattering. Impurity scattering is due to both intentional dopant impurities and unwanted impurities.

Lattice scattering is due to vibrations and imperfections in the crystal lattice. The trapping of charge carriers depends on the energy of the charge carrier at the trapping/impurity atom. The carrier is trapped if its energy is lower at the trapping site than anywhere else. The electric drift current density in an semiconductor is

$$J_{\text{drift}} = (qn\mu_n + qp\mu_p) \mathcal{E} = \sigma \mathcal{E}$$

(2.1)

where  $\sigma$  is defined as the conductivity,  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities respectively, n and p are the carrier concentrations of electrons and holes respectively, q is the electron charge and  $\mathcal{E}$  is the electric field strength. Carrier diffusion is due to a carrier concentration gradient in the semiconducting material. The diffusion current density is

$$J_{\text{diff}} = qD_n \frac{dn}{dx} - qD_p \frac{dp}{dx} \tag{2.2}$$

where  $D_n$  and  $D_p$  are the electron and hole diffusion coefficients respectively. The total current density due to drift and diffusion is

$$J_{\text{total}} = J_{\text{drift}} + J_{\text{diff}}$$

(2.3)

$$= (qn\mu_n + qp\mu_p)\mathcal{E} + qD_n\frac{dn}{dx} - qD_p\frac{dp}{dx}$$

(2.4)

$$= \left(qn\mu_n\mathcal{E} + qD_n\frac{dn}{dx}\right) + \left(qp\mu_p\mathcal{E} - qD_p\frac{dp}{dx}\right). \tag{2.5}$$

In solar cells, excess carriers are introduced by optical absorption of the semiconducting material, a process often called carrier injection. In this situation, the system is not in thermal equilibrium, that is,  $pn > n_i^2$ , where  $n_i$  is the intrinsic carrier concentration. For equilibrium to be regained, minority and majority carriers recombine. The dominating recombination process for silicon is an indirect

process because of the indirect band-gap of silicon. When a semiconductor material is illuminated, electron-hole pairs are generated with a rate  $G_{\rm L}$ . At equilibrium, the generation rate is equal to the recombination rate,  $G_{\rm L}=R=G_{\rm th}$ . The net recombination rate is  $U=R-G_{\rm th}$  and is equal to zero at thermal equilibrium. For holes in an n-type semiconductor, the net recombination rate is proportional to the excess minority carrier concentration, or

$$U = \frac{p_n - p_{n0}}{\tau_p} \tag{2.6}$$

where  $\tau_p$  is the minority carrier lifetime and is a measure of how fast majority and minority carriers recombine,  $p_{\rm n}$  is the minority carrier concentration and  $p_{\rm n0}$ is the minority carrier concentration at thermal equilibrium. The minority carrier lifetime is an important parameter for solar cells as it is used as a measure of the quality of the cell. The minority carrier lifetime can be estimated by illuminating a semiconducting sample and measure the open-circuit voltage decay. If a short light pulse is used to illuminate an n-type semiconductor, then the minority carrier concentration after the light pulse is turned off is

$$p_n(t) = p_{n0} + \tau_p G_L \exp(-t/\tau_p).$$

(2.7)

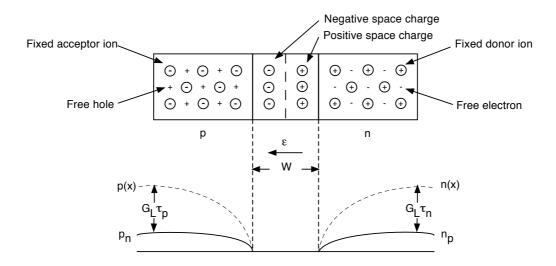

Figure 2.6 shows a schematic of a p-n junction along with a graph that shows the minority carrier concentration in the n- and p-side of the junction respectively, with and without light injection. For solar cells, it is important that the recombination does not occur before the carriers reach the p-n junction. The method used to measure the minority carrier lifetime will be discussed in chapter 3.4. The relation between diffusion length  $L_{\rm p}$  of holes in the n-type semiconductor and the minority

carrier lifetime is given by

$$L_{\rm p} = \sqrt{D_{\rm p}\tau_{\rm p}} \tag{2.8}$$

where  $D_{\rm p}$  is the diffusion coefficient of holes. The short-circuit current in solar cells can decrease due to the recombination of charge carriers at a boundary (Zook, 1980). As the grain size decreases, electrical parameters such as minority carrier lifetime decrease (Yamazaki et al., 2006).

#### p-n junction

A junction of opposite charge carrier types can be created in semiconductors. When the junction is formed, the electrons diffuse to the p-side and holes diffuse to the n-side. This is due to carrier concentration gradients near the junction. Uncompensated donor and acceptor sites are left behind in the n- and p-side, respectively. Donors on the n-side are ionized and thus positively charged. Similarly, on the p-side, acceptors are ionized and thus negatively charged. This creates an electric field in that region which is called the space-charge region or depletion region. The potential difference between the n- and p-side is called the built-in potential. It depends upon the doping concentrations in the p-type and n-type semiconductor materials. The width of the depletion region also depends on the doping concentration.

When the p-side of a p-n junction is at a higher potential than the n-side, that is the junction is forward biased, minority carriers are injected into each side. The potential across the depletion region is lowered and the current across the junction consists mainly of diffusion. Under reverse bias, the built-in voltage is raised and the resulting drift current is very small and is referred to as reverse current. Figure 2.7 visualizes an energy band diagram for a p-n junction in thermal equilibrium. The potential barrier between the n- and p-side is  $qV_{\rm bi}$ . The ideal diode equation

gives the current through the p-n junction for forward and reverse bias

$$I = I_{\rm s} \left( \exp\left(qV/nkT\right) - 1 \right) \tag{2.9}$$

where n is the ideality factor and  $I_s$  is the reverse saturation current, given by

$$I_{\rm s} = qA \left( \frac{D_{\rm p}p_{\rm n}}{L_{\rm p}} + \frac{D_{\rm n}n_{\rm p}}{L_{\rm n}} \right). \tag{2.10}$$

### Solar cells and photodiodes

When a photon hits a semiconductor surface, an electron in the valence band can be excited into the conduction band. This process is called photon absorption and is strongest when the electron can go directly to the conduction band. For semiconducting materials with an indirect bandgap, lattice vibration are required to assist in the process. The absorption coefficient  $\alpha$  describes the ability of the

**Figure 2.6:** Minority carrier concentration in an p-n junction with (dashed line) and without (solid line) light injection.

Figure 2.7: An energy band diagram of an p-n junction in thermal equilibrium.

material to absorb photons. Below the bandgap energy  $E_{\rm g}$  the semiconductor is transparent and the absorption coefficient is zero. Similarly above a specific cutoff wavelength  $\lambda_{\rm c}$  the absorption coefficient is zero. It is given by

$$\lambda_{\rm c} = \frac{1.24}{E_{\rm g}} \tag{2.11}$$

where  $E_{\rm g}$  is in eV and  $\lambda_{\rm c}$  is in  $\mu{\rm m}$ . The band gap energy of silicon is 1.12 eV at room temperature. Therefore photons with energy less than the bandgap energy of silicon are not absorbed. Photon energy higher than 1.12 eV corresponds to wavelengths less than 1.11  $\mu{\rm m}$  and therefore ranges from the near-infrared to the ultra-violet region. When photons of energy larger than the band gap energy of the semiconductor, hit the surface of a semiconductor, electron-hole pairs are generated. Photons of energy that is much larger than the bandgap energy of the semiconductor lose part of their energy as heat. For absorbed photons in the

semiconductor, the carrier generation rate is

$$G_{\rm L} = \frac{\alpha P_{\rm op}}{\hbar \omega} = \alpha J_{\rm ph}(x)$$

(2.12)

where  $J_{\rm ph}(x)$  is the photon flux,  $P_{\rm op}$  is optical power per unit area,  $\alpha$  is the absorption coefficient and  $\hbar\omega$  is the photon energy. This is referred to as photoconductivity. The responsivity of the semiconductor to incoming photons is given by (Singh, 2001)

$$R_{\rm ph} = \frac{J_{\rm L}}{P_{\rm op}} \tag{2.13}$$

where  $J_{\rm L}$  is the resulting photocurrent density. The absorption coefficient  $\alpha$  for direct bandgap materials is typically a factor of 100 higher than for indirect bandgap materials (Singh, 2001).

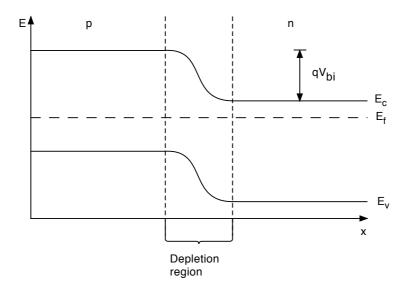

A p-n junction solar cell is in principle composed of a p-n junction near the surface of the diode (shallow junction) and ohmic contacts to the front and back of the diode. A schematic of a solar cell is shown in figure 2.8. The ohmic contacts on the front surface are called bus bars and are used to provide ohmic contacts with minimum series resistance and without shadowing the incoming radiation. The junction must be near the surface of the grown film for most of the minority carriers to be able to reach the junction before they recombine with the majority carriers. If a minority carrier reaches the junction, it is swept across the junction by the electric field resulting in an electric current. The diffusion length of the minority carriers is a measure of how far they diffuse before recombining. Therefore it is required that the diffusion length is larger than the distance from where they are created, to the junction. The power solar cells can convert is proportional to the power of the incident light and the area of the cell. Photodiodes as well as solar cells are based on p-n junctions that collect the carriers that are injected into one side. The

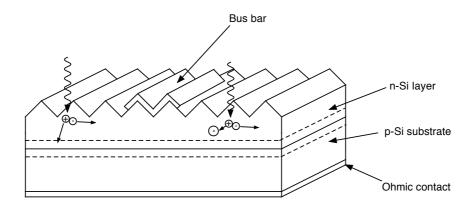

minority carriers diffuse to the space charge region of the junction and are swept across this region by the built-in electric field. The difference between solar cells and photodiodes is that the photodiode requires reverse bias for its operation. Thus photodiodes operate in the first quadrant of the I-V characteristics while solar cells operate in the third quadrant. Figure 2.9a shows a typical I-V characteristic for a solar cell. Figure 2.9b shows the I-V characteristic in the fourth quadrant after inversion about the voltage axis.

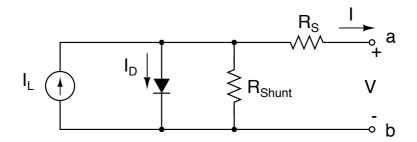

An equivalent circuit of a solar cell and a load connected to it is seen in figure 2.10. The current through the solar cell is given by (Schwartz, 1993)

$$I = I_{\rm L} - I_{\rm s} \left( \exp\left(\frac{q(V + IR_{\rm s})}{nkT}\right) - 1 \right) - \frac{V + IR_{\rm s}}{R_{\rm shunt}}$$

(2.14)

where  $I_s$  is the reverse saturation current, V is the voltage across the cell, n is the ideality factor and  $I_L$  is the photon induced current. The ideality factor is equal to 1 for an ideal diode and increases as the quality of the diode decreases.

**Figure 2.8:** A schematic of a p-n junction solar cell along with the front and back ohmic contacts. On the left an incoming photon generates an electron-hole pair, the hole diffuses across the junction and contributes to the current. On the right, the hole from the generated electron-hole pair is trapped by an impurity and does not contribute to the current.

Figure 2.9: Figure (a) shows the I-V characteristics of a solar cell with (dashed line) and without illumination (solid line). Figure (b) shows quadrant IV and the solid blue line shows the I-V characteristics for an ideal solar cell. The dashed green line shows the I-V characteristic for a solar cell with  $R_{\rm S}=5\,\Omega$  and  $R_{\rm shunt}=1\,{\rm M}\Omega$ . The square shows the area where maximum power can be drawn from the device.

$R_{\rm s}$  represents the series resistance of the diode and  $R_{\rm shunt}$  represents the diodes internal characteristic. For an ideal diode,  $R_{\rm s}=0$  and  $R_{\rm shunt}=\infty$ . The series resistance results from ohmic losses in the front surface. A series resistance of  $5\,\Omega$  can reduce the available power by 30% compared to the ideal case (Sze, 2002). The series resistance depends on the depth of the junction, the impurity concentration in the p- and n-regions and the arrangement of the ohmic contacts. An increase in  $R_{\rm s}$  causes a reduction in V and  $I_{\rm sc}$ . Low values in  $R_{\rm shunt}$  can be caused by an increased conductance through the diode. This has the effect of decreasing the current and reducing the open-circuit voltage. The ideality factor of the solar cell can be estimated by calculating the slope m of the positive part of  $\ln I$  as a function of applied voltage. Then the ideality factor is calculated as

$$n = \frac{q}{kTm}. (2.15)$$

Figure 2.10: Equivalent circuit of a solar cell.  $I_{\rm L}$  is the photon induced current,  $I_{\rm D}$  is the ideal diode current,  $R_{\rm S}$  is the series resistance and  $R_{\rm shunt}$  is the shunt resistance of the diode.

For an ideal diode, the open circuit voltage (I=0) is

$$V_{\rm OC} = \frac{kT}{q} \ln \left( \frac{I_{\rm L}}{I_{\rm s}} + 1 \right) \tag{2.16}$$

and the power that the solar cell absorbs and converts is

$$P = IV = I_{\rm L}V - I_{\rm s}V \left(\exp\left(\frac{qV}{nkT}\right) - 1\right). \tag{2.17}$$

The maximum power  $P_{\rm m}$  is absorbed when dP/dV=0, or at  $P_{\rm m}=I_{\rm m}V_{\rm m}$ . The power conversion efficiency is given by

$$\eta = \frac{I_{\rm m}V_{\rm m}}{P_{\rm in}} \tag{2.18}$$

or

$$\eta = \frac{\text{FF} \cdot I_{\text{SC}} V_{\text{OC}}}{P_{\text{in}}} \tag{2.19}$$

where  $P_{\rm in}$  is the solar power incident on the cell and FF is the so called fill factor defined as

$$FF = \frac{I_{\rm m}V_{\rm m}}{I_{\rm SC}V_{\rm OC}}.$$

(2.20)

For the efficiency to be maximized, the product of FF and  $I_{\rm L}V_{\rm OC}$  has to be maximized (Schwartz, 1993). For most solar cells, the fill factor is FF  $\approx 0.7$ . Hötzel et al. (2000) discusses how the fill factor can be optimized. The thermodynamic efficiency limit describes how photons with energy greater than the band-gap of the silicon can be converted to electricity, while photons with energy well above the band-gap are mostly converted to heat. Only a fraction of the photons with energy above the band-gap are converted to electricity, and the rest is converted to kinetic energy. This problem can be partially solved by utilizing multiple band-gap absorber materials which increases this efficiency (Schwartz, 1993). Quantum efficiency is referring to the part of the photons that are converted to electric current. Internal quantum efficiency is the fraction of absorbed photons that are converted to electric current, while external quantum efficiency is the fraction of incident photons that are converted to electric current.

## 2.6 Creation of an active layer

From the 1950s and onwards, p-n junctions are typically fabricated by diffusion of impurities or dopants into a bulk material which can be silicon. This can be done in various ways, for example by placing a silicon wafer inside a chamber along with a gas that contains an impurity that would act as an acceptor or a donor and thus give the appropriate doping. By annealing for specific amount of time, the dopant diffuses a certain distance into the substrate. One disadvantage of this method is that the p-n junction will be graded instead of abrupt. In addition, if the substrate is poly-crystalline, the dopants can diffuse faster along the grain boundaries, creating channels of dopants. Consequently the depth of the junction and the thickness of the solar cell will be relatively large which will lower the efficiency due to recombination of electrons and holes.

30 Silicon solar cells

Another method is ion implantation, in which the dopant ions are accelerated into the grown silicon film. A disadvantage of this method is that the surface gets damaged during the ion bombardment. This can be partially fixed by annealing the substrate which in turn drives the junction deeper into the substrate, which is an disadvantage for solar cells because the junction has to be close to the surface in order for the charge carriers to reach the junction before they recombine.

A p-n junction can also be fabricated by growing a doped thin film semiconductor on top of a substrate of the opposite doping type. This is the method discussed here.

# Chapter 3

# Experimental methods and apparatus

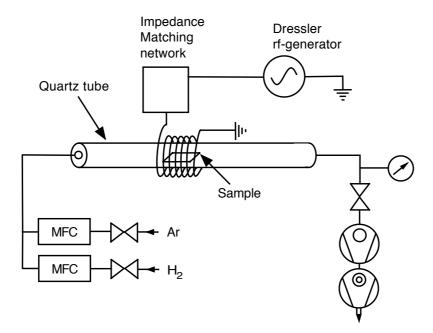

Here, the instruments and equipment used as well as the methods applied for the thin film growth and thin film characterization are described. First, the liquid phase epitaxy (LPE) technique is discussed in general and then its applications to silicon thin film growth. Subsequently, hydrogenation of the grown films is discussed. An overview of the electrical characterization is given, including the measurements of minority carrier lifetime and the Hall and conductivity measurements that give the carrier concentration and mobility, respectively. A scanning electron microscope (SEM) and an atomic force microscope (AFM) are used to assess the film morphology. Finally the crystallinity of the films and substrates are characterized using X-ray diffraction (XRD).

## 3.1 Liquid phase epitaxy

Liquid-phase epitaxy (LPE) is a method to grow crystalline layers from a melt on solid substrates. The melt is usually a metal which can dissolve the needed amount of the growth material. Common solvents used for silicon growth include tin (Sn), gallium (Ga) and indium (In). A more thorough discussion of solvents in silicon LPE will be in section 3.1.3. In principle, LPE can be applied to any chemical system where a sufficient amount of solute material can be precipitated from the solvent during cooling. In this way a film can be formed on a substrate.

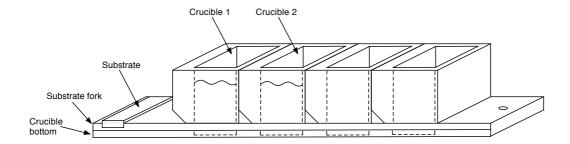

Many variations in LPE growth exists (Astles, 1990; Scheel, 2007). These include the vertical dipping method, where the substrate is dipped into the metal solution and the slider-boat method, where the substrate is dragged through crucibles which contain appropriate liquid metal solutions. In the slider-boat method, the substrate is held in place with a special kind of a fork. Crucibles are lined up and the substrate can be dragged under the crucibles for the substrate to come into contact with the materials contained in the crucibles. The crucibles and the fork are usually made of graphite because it can withstand high temperatures without decomposing and contaminating the growth. This method is suitable for laboratory use but not for large-scale production. The dipping method is more suitable for large-scale production because the crucibles and substrates can be very large and thus larger batches can be produced.

LPE is not suitable for growing layers in the nanometer thickness scale due to the high surface tension of metallic solutions of semiconductors (Scheel, 2007). Therefore it cannot be used for fabrication of transistors or other similar delicate structures. Furthermore, LPE is not suitable for applications that require large-area uniformity, critical layer thickness and composition control. Other techniques such as chemical vapor deposition (CVD), molecular beam epitaxy (MBE) and

metal-organic vapor phase deposition (MOVPE) are often chosen instead and are discussed in section 3.1.1. The LPE technique offers many advantages over other deposition methods. It is simple and the operating and equipment costs are relatively low. The films are of good quality with low contamination levels even when grown at relatively low temperatures. Low density of structural defects and low recombination activity at grain boundaries can be obtained if the growth conditions are suitable. Furthermore, LPE offers high deposition efficiency. The technique was originally invented to overcome limitations of substrate quality as well as the limitations of the CVD technique (Mauk, 2007). There are no toxic precursors or byproducts involved with the LPE process as for instance in MOVPE and CVD, and the quality of the grown layers with respect to minority carrier lifetimes and recombination lifetimes, is high, which is important for solar cell applications (Mauk, 2007). LPE can be a suitable method for thin film growth on low-cost substrates. The substrate can be in-situ etched by partial dissolution of the substrate in the metal solvent, often referred to as melt-back. If the slider-boat technique is used, this can be implemented by dragging the substrate under a crucible containing a metal solvent partly saturated with the growth material. This can improve the wetting of the substrate before growth and reduce the occurrences of so called growth pyramids. Growth pyramids are due to twinning which is often initiated at the substrate surface (Ghandhi, 1983). Pyramidal textures can though be of use in light entrapment as demonstrated by Konuma et al. (1994) which had success with growing pyramidal and roof shaped textures on silicon for these purposes.

LPE has mostly been used for growing GaAs, GaP and AlGaAs thin films, and also silicon on a variety of substrates (Mauk, 2007). For solar cell applications the substrate can be for example single-crystalline (Zheng et al., 1996; Arch et al., 1993; Majumdar et al., 2003), poly-crystalline (Steiner and Wagner, 1995), upgraded

metallurgical grade silicon (Ciszek et al., 1993; Hötzel et al., 2000; Peter et al., 2002; Kopecek et al., 2001; Müller et al., 2003) and with a porous sacrificial silicon layer (Fave et al., 2008). Abrupt p-n junctions can be created when growing films with the LPE method. A wide range of dopants are available. The growth temperature can be well below the melting point of the growth material, which is of great importance since high temperatures can cause decomposition of the substrate. A disadvantage of using LPE for growing silicon thin films is that the solubility of silicon in many metallic melts is low and there can be high content of the solvent incorporated into the grown film. To reduce material costs, the solvents can in principle be reused.

One restriction to the use of LPE is the limited amount of lattice mismatch between the substrate and the grown layer which can be tolerated. The lattice mismatch is defined by

$$\mathcal{E} = 2\frac{a_{\rm l} - a_{\rm s}}{a_{\rm l} + a_{\rm s}} \tag{3.1}$$

where  $a_1$  and  $a_s$  are the lattice parameters of the layer and substrate respectively. If  $\mathcal{E} > 10^{-3}$  then an increasing tendency towards the generation of misfit dislocations and an increasing difficulty in nucleating the epitaxial layer growth is expected (Astles, 1990). The effects of thermal mismatches are increased when the silicon layer is grown on a foreign substrate (Abdou et al., 2005). Such lattice mismatch is most easily avoided by growing film with similar or same lattice parameter as the substrate. The MG-Si substrate that is being used in our case can be considered a foreign substrate to a certain degree.

A summary of the main advantages and disadvantages of LPE is given in table 3.1.

**Table 3.1:** An overview of the advantages and disadvantages of liquid-phase epitaxy for the growth of silicon thin films.

| Advantages                                                                                                                                                                                                                                                                                                                                       | Disadvantages                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High quality of grown films Relatively low growth temperatures compared to other methods Abrupt junctions High growth rates compared with other thin-film techniques High deposition efficiency, and low equipment and operating costs No toxic precursors In-situ etching of silicon and in-situ doping Wide range of dopants Reusable solvents | Solubility of silicon in many metallic melts is low  High content of solvent can be incorporated into the grown film  Hard to control layer thickness and uniformity  Not suitable for growing layers in nanometer scale  Only a small lattice mismatch between substrate and film is tolerated  Difficult to monitor the growth process directly  Non-uniform thickness |

#### 3.1.1 Alternatives to LPE

When selecting a method for epitaxial growth of specific materials and for particular applications, some practical considerations must be followed. They include capital investment, operating costs, safety, reproducibility, required skill and controllability with respect to thickness and doping (Astles, 1990). A number of methods are currently being used for both research and production of solar cells. These include MBE, MOVPE and CVD. In the recent years, the requirement of large area uniformity, critical layer thickness and composition control, smooth surfaces and abrupt interfaces, has pushed the LPE technique off the market replacing it by MBE and MOVPE which can fulfill the requirements. There is though a constant development of the LPE technique and control over the grown layer thickness is improving.

In LPE the composition of the layer is determined by phase equilibria and thus exhibits a low thermodynamic driving force. Consequently better control of nucleation is obtained which is necessary for selective modes of growth, it also lowers the possibility of nucleation on non-equilibrium defects such as stacking faults and dislocations.

MBE is a method for epitaxial growth based on reactions of thermal beams of atoms or molecules with a crystalline substrate under a high vacuum. MBE is precise in both chemical compositions and doping profiles. Multilayer structures with thickness on the order of atomic layers can be grown. However, the deposition rate is very low.

CVD, often referred to as vapor phase epitaxy (VPE), is a method in which epitaxial layers are grown by reactions between gaseous compounds. Metal-organic vapor phase epitaxy (MOVPE) varies from the traditional CVD as it is based on surface reactions of metal organic compounds and metal hydrides. MOVPE has mostly been used for heteroepitaxial growth of III–V and II–VI compounds. CVD is a costly and complex method for deposition of silicon (McCann et al., 2001). CVD is scalable and generally allows fabrication of high quality layers. However, at low temperature (< 600°C) the deposition rate is low.

MBE and CVD exhibit high thermodynamic forces which as useful for heteroepitaxial growth where there is strain or lattice mismatch that inhibits nucleation of the epitaxial layer. In particular the cost of precursor and dilutant gases is substantial. Most deep level impurities have low segregation coefficients. As a result, epitaxial layers grown with LPE have been shown to have lower deep level incorporation than CVD for example (Ghandhi, 1983). MOVPE offers better control over the grown layer thickness, doping concentration, abruptness of grown interfaces and alloy composition. MBE and MOVPE offer higher supersaturations than possible

in LPE. Higher supersaturation makes it possible to grow single-crystalline films on substrates with high lattice mismatches ( $\mathcal{E} < 10^{-1}$ ) or with different crystal structures (Astles, 1990). Growth rate by LPE can be 10-100 times faster than by MBE or CVD and the whole process can be more flexible. Generally, CVD has more experimental parameters than LPE, but a broad operating range. Thus, the LPE method is more susceptible to process fluctuations and the effects of uncontrolled parameters. Both can lead to failed growth or poor material quality. LPE appears to be more sensitive to the crystallographic orientation of the substrate than other epitaxy techniques. When the controllable parameters for LPE growth are within its optimum range, the material quality of the grown layers can be superior to that produced by other epitaxy techniques. Although LPE has not been considered suitable for large scale production, recent modifications have changed the situation (Müller et al., 2003; Weber et al., 2003).

### 3.1.2 Doping and precipitation from the liquid phase

Almost any solids, liquids or gases that come into contact with the substrate at the growth temperature will be incorporated into the grown film to a certain degree. This emphasizes the fact that the choice of solvent and other ingredients that are used is very important. In some cases, the solvent itself acts as a dopant in the grown film. Types of solvents for silicon LPE will be discussed further in section 3.1.3. A segregation coefficient  $k_i$  is a measure of how much of the impurities are incorporated into the solid from the melt. As the starting materials for LPE growth are normally of high purity, the easiest way for impurities to enter the system is through partial substrate dissolution, or melt-back. This improves the wetting of the substrate and helps by removing the native oxide of the substrate. The segregation coefficient of impurities from metal solvents to solid silicon in the

temperature range  $800 - 1000^{\circ}$ C is given by

$$k_{\rm i} = \frac{C_{\rm i}^{\rm S}}{C_{\rm i}^{\rm L}} = k_{\rm i,0} \cdot \exp\left(-\frac{b_i}{T}\right) \tag{3.2}$$

where  $C_i^{\rm S}$  is the impurity concentration in the solid silicon,  $C_i^{\rm L}$  is the impurity concentration in the liquid, T is the temperature of the liquid and  $k_{\rm i,0}$  and  $b_i$  are constants that are specific to each impurity. It depends on the solvent used whether melt-back is necessary, but Gee and Ciszek (1996) report on using a Cu/Al solvent that is able to wet the substrate without melt-back. In the case of using a silicon substrate, the substrate is often etched in a diluted hydrofluoric acid before growth to ensure an oxide free surface. For trivalent solvents such as gallium and indium, their segregation coefficient is relatively high in silicon and therefore they will act as p-type dopants. Tin and lead are iso-electronic with silicon and therefore will not provide charge carriers in the crystal.

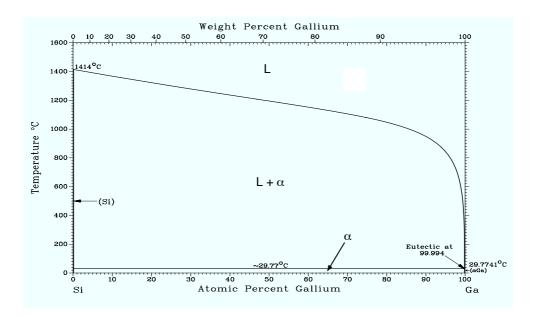

An equilibrium binary phase diagram describes the relationship between the compositions of the components and the temperature of the system while the pressure is a constant. In LPE, phase diagrams are useful in determining the solubility of a solute in a specific solvent over a specific temperature range. Additionally they give indication of the behavior of the system with temperature. The Si-Ga phase diagram is shown in figure 3.1. Above the liquidus line, only liquid phase (L) exists and below the solidus line, only a solid phase ( $\alpha$ ) exists. Between the liquidus and solidus lines is a region in which both liquid and solid phases (L +  $\alpha$ ) can exist. The solidus line in the phase diagram gives information about the degree of incorporation of the component into the solid (Mauk, 2007). The slope of the liquidus line gives the temperature range for growth to occur. Additionally it gives information on how much of the growth material can be precipitated from the solvent. Typically, the solubility of semiconductors such as silicon in metals

Figure 3.1: The Si-Ga phase diagram which shows the relationship between component concentration and temperature at a constant pressure (ASM, 2008). Above the liquidus line is a liquid phase (L), between the liquidus and solidus lines is a combination of a liquid phase and a solid phase (L+ $\alpha$ ), and under the solidus line is only a solid phase ( $\alpha$ ).

#### increases with temperature.

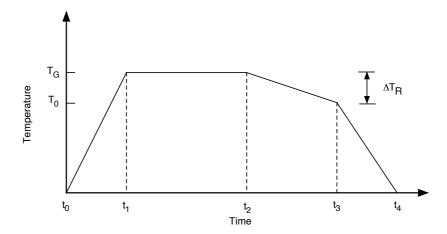

The solvent is saturated with the solute at the liquidus temperature  $T_{\rm L}$ . The driving force of the growth is the supersaturation of the solvent by the solute. The supersaturation can be obtained in different ways. Ramp cooling is based on saturating the solvent at the growth temperature  $T_{\rm G} = T_{\rm L}$  and decreasing the temperature of the system by  $\Delta T_{\rm R} = T_{\rm G} - T_0$  with a fixed rate R [°C/min]. In this case the substrate is brought into contact with the solution while the solution is being either saturated with sacrificial silicon or silicon that originates in the substrate. This takes place in the time interval between  $t_1$  and  $t_2$  as shown in figure 3.2. This allows for the solvent to become fully saturated with the solute if it was not before. A larger supersaturation is obtained with the supercooling technique. There the supersaturation of the solvent is increased by decreasing the

**Figure 3.2:** Temperature-time profile for ramp-cooled LPE growth. Initially the system is heated up to the growth temperature  $T_g$ . At  $t_1$  the growth solution is saturated with the solute at the temperature  $T_g$ . At  $t_2$  the growth starts and ends at  $t = t_3$ . Between the time  $t_3$  and  $t_4$  the system cools down.

temperature of the system by  $\Delta T_{\rm S} = T_{\rm L} - T_{\rm G}$ . The substrate is then brought into contact just before the temperature is decreased by  $\Delta T_{\rm R} = T_{\rm G} - T_0$  with a fixed rate R [°C/min]. The supersaturation is relieved by precipitation of the solute on a substrate. It is important that there is no excessive silicon present in the saturated melt at the liquidus temperature. The silicon would then act as a nucleation center and compete with the substrate, possibly result in low surface coverage of the grown film. The growth temperature is known to affect the lifetime of minority carriers in LPE grown films. At growth temperatures above 800°C, the minority carrier lifetime decreases drastically as the growth temperature increases (Satoh et al., 2005). It was shown that this reduction in minority carrier lifetime was due to high incorporation of the solvent at higher temperatures. Peter et al. (2002) reports on obtaining smoother layers when the cooling rates are relatively low ( $\leq$  1°C/min).

#### 3.1.3 Silicon LPE

#### Solvents and dopants

When choosing the solvents for epitaxial growth of silicon thin films, there are several criteria that can be used as guidelines (Mauk, 2007).

- The melting point of the solvent has to be relatively low and should be able to dissolve the needed amount of silicon.

- The wetting of the substrate is an important factor in order to obtain a continuous layer.

- There must be low reactivity between the crucible material and the solvent.

- It is preferred that the solvent is non-toxic or at least low in toxicity.

- There must be a simple and versatile way to remove the remains of the solvent from the surface of the grown film.

- The electrical properties of the metal or any metals that are dissolved in the solvent must be known. They can either be iso-electrical or electrically active.

Table 3.2 gives an overview of solvents that can be used for silicon LPE growth. The solvent and any impurities that are dissolved in the melt are incorporated into the grown silicon film, to a certain degree. These impurities are either added to intentionally dope the deposited layer or they can originate in the substrate or from other sources. The melt can also remove impurities that could have resided on the surface of the substrate. Impurities that belong to groups III and V of the periodic table are substitutional diffusers in silicon with the exception of indium (In). The dopants from group III and V are all shallow donors and shallow acceptors in silicon, respectively. Impurities from group I and group VIII take up interstitial sites in

silicon and are usually electrically inactive. An exception is lithium which acts as donor in silicon. Elements such as cobalt, copper, gold, iron, nickel, platinum and silver diffuse by an interstitial-substitutional mechanism in silicon and can end up in both types of sites. All of these impurities are known to reduce minority carrier lifetime in silicon. Silver and gold are deep lying impurities in silicon and gold has been used effectively to reduce minority carrier lifetime in silicon for specialized applications (Ghandhi, 1983).

The solubility of silicon in various metal solvents depends on the nature of the solvent and the temperature. For growing relatively thick silicon films, higher temperatures are required, which on the other hand lowers the minority carrier lifetime (Abdou et al., 2005). Among well known solvents used in silicon LPE are tin (Sn), lead (Pb), gallium (Ga), indium (In), aluminum (Al), bismuth (Bi), antimony (Sb), gold (Au) and copper (Cu). Table 3.2 gives an overview of the previously mentioned solvents, along with some of their properties at 900°C. Impurities such as boron (B) can be difficult to remove from silicon since its segregation coefficient is high compared to other elements as shown in table 3.2.

**Table 3.2:** Overview of the growth relevant properties of metal solvents for silicon LPE growth for a growth temperature of 900°C (Sze, 2002).

| Metal solvent | Melting point [°C] | Segr. coeff.               | Solubility $[cm^{-3}]$ | Doping |

|---------------|--------------------|----------------------------|------------------------|--------|

| Aluminum (Al) | 660                | $2 \times 10^{-3}$         | $1 \times 10^{19}$     | p      |

| Antimony (Sb) | 630.8              | $2.3 \times 10^{-2}$       | $3 \times 10^{19}$     | n      |

| Bismuth (Bi)  | 271.4              | $7 \times 10^{-4}  ^{[1]}$ | $2 \times 10^{16}$     | n      |

| Copper (Cu)   | 1083.2             | $4 \times 10^{-4}$         | $1 \times 10^{17}$ [2] | -      |

| Gallium (Ga)  | 29.8               | $8 \times 10^{-3}$         | $2 \times 10^{19}$     | p      |

| Indium (In)   | 156.2              | $4 \times 10^{-4}$         | $2 \times 10^{16}$     | p      |

| Tin (Sn)      | 231.9              | $1.6 \times 10^{-2}$       | $4 \times 10^{19}$     | -      |

<sup>[1]:</sup> Morvan and Amouroux (1981)

<sup>[2]:</sup> Ghandhi (1983)

#### Growth and substrates

Abdou et al. (2005) studied LPE growth from tin alloys (Sn-Al, Sn-In) at 800°C and reported that adding a trace amount of aluminum to the solvent helps with removing the native oxide of the substrate. For the aluminum not to heavily dope the grown layer, it must be added to a separate melt. Better morphology was obtained with a higher content of Sn in the Sn-In system, but voids on the substrate were existent when using an In rich solvent. Konuma et al. (1995) reports on layer growth on single crystalline silicon substrates with Ga and Ga-In solvents at temperatures below 450°C. Growth from the Ga-In alloy results in a p-type doped layer with carrier concentration that is 50% of the concentration obtained by a Ga solvent alone. Peter et al. (2002) studied the effect of gallium concentration in the In-Ga system on the layer characteristics. A 0.1% wt Ga with In melt resulted in a carrier concentration of around  $10^{17}\,\mathrm{cm}^{-3}$  and a smooth layer. The electrical characteristics depended heavily on the growth rate as the mobility and minority carrier lifetime increased as the cooling rate was lowered. Arch et al. (1993) also grew p-type Si layers from In-Ga solvent with carrier concentrations in the range  $10^{16} - 5 \times 10^{19} \,\mathrm{cm}^{-3}$ . They claim the quality of their films is comparable to that of float zone silicon. Similarly, Zheng et al. (1996) used Ga doped In melt to grow Si film for a highly efficient solar cell. Tin and lead are electrically neutral in silicon and for that reason they are often chosen as solvents. The presence of tin in the melt will though have effect on the electrical parameters as the presence of tin is known to decrease minority carrier lifetime. Weber et al. (2003) report that a significant reduction in minority carrier lifetime is observed in thin films grown from a tin solvent when compared with films grown from an indium solvent. The market supply of solvents is also an important factor when selecting solvents. Weber et al. (2003) mentions that a limited availability of indium causes problems when

upscaling. Ciszek et al. (1993) studied LPE growth of thin film silicon from alloy solvents that included Cu, Al, Al-Cu, Bi, Ga-Cu and Sn solutions at temperatures below 950°C.

Some of the problems that arise when growing Si thin films on multi-crystalline MG-Si substrates include

- rough surfaces from growth rate variation due to variable grain orientation

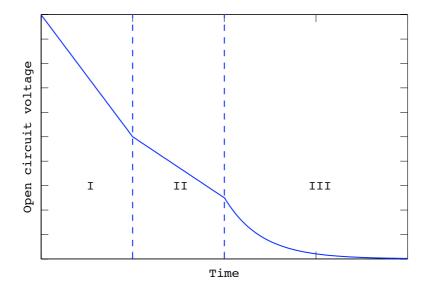

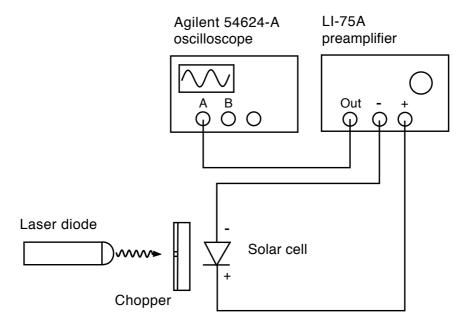

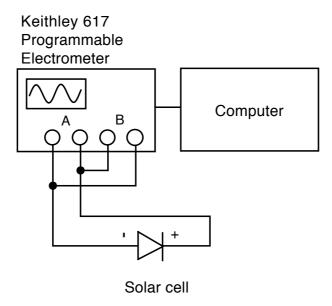

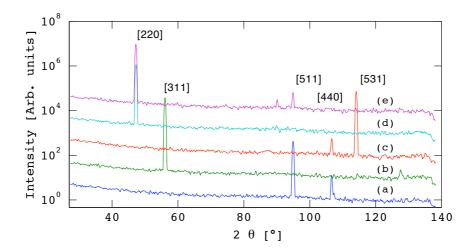

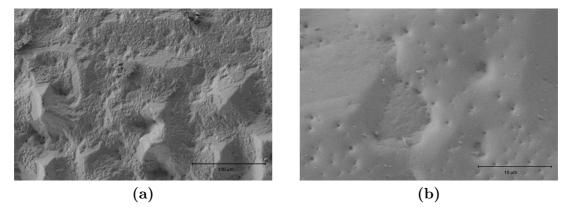

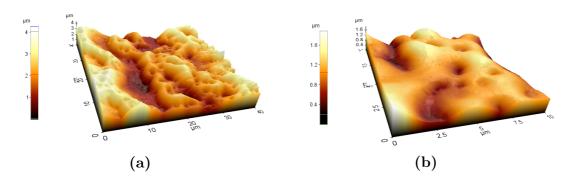

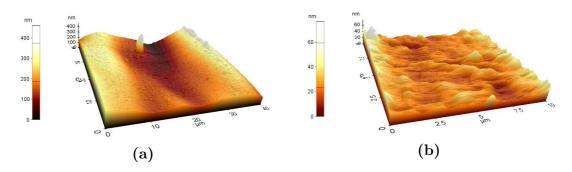

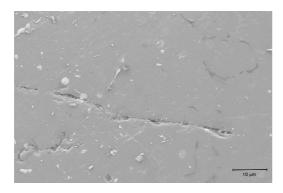

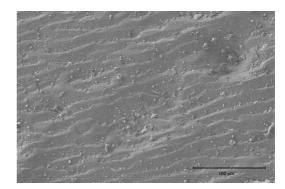

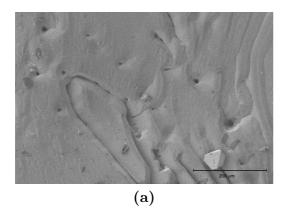

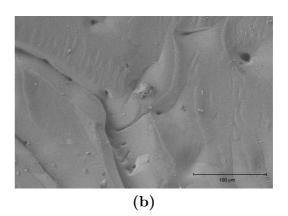

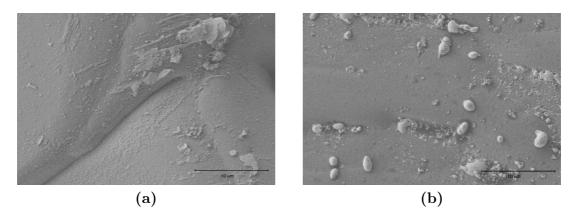

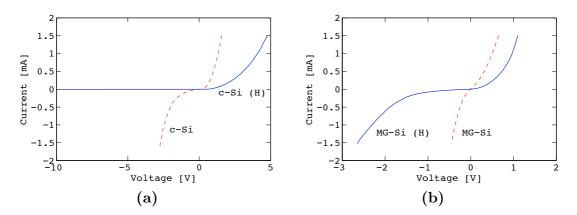

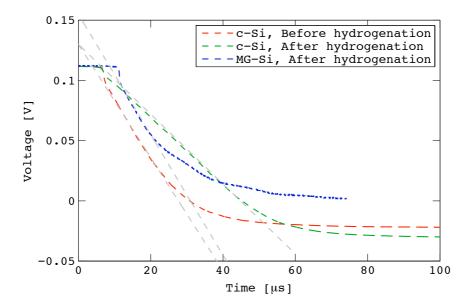

- impurity contamination from the MG-Si substrate